# FPGA Based Analysis of Non-Deterministic PWM in Induction Motor Drives

Prof.T.Jarin<sup>1</sup> and Prof.X.Z.Gao<sup>2</sup>

<sup>1</sup>Associate Professor, Department of EEE, Jyothi Engineering College, Under KTU, Kerala, India.

Article Received: 30 August 2017

Article Accepted: 17 September 2017

Article Published: 22 September 2017

## **ABSTRACT**

The prime advantage of non-deterministic Pulse Width Modulation (PWM) strategies is that the harmonic spectrum of the output voltage is spread over a range without any specific dominant harmonic. This absence of distinct dominant harmonics results mainly in reduction of acoustic noise and torque ripples in drives. In this paper, a Field-Programmable Gate Array (FPGA) based implementation and corroboration of Pseudo Random Binary Sequence (PRBS) bit based Random Carrier PWM (RPWM) for the three-phase Voltage Source Inverter (VSI) fed induction motor drive, are presented. First, a detailed simulation study on performance characteristics such as harmonic spectrum, Total Harmonic Distortion (THD), Harmonic Spread Factor (HSF) and power density spectrum, are presented for both conventional Sinusoidal PWM (SPWM) and RPWM. Secondly, a new circuit realization of the above PWM strategies are developed using state of-the-art FPGA technology. The designed controller provides a simple and effective solution for high-performance AC drives.

Keywords: Field Programmable Gate Array (FPGA), Harmonic Spread Factor (HSF), Power Density Spectrum, Random Pulse Width Modulation (RPWM) and Voltage Source Inverter (VSI).

#### 1. Introduction

Pulse-Width Modulated (PWM) Voltage Source Inverters(VSIs) represent the dominant technology in industry today [1]-[3]. A large number of PWM switching pattern generators have been developed over the last four decades to meet the respective requirements for distortion free output waveforms of sinusoidal nature. Overall system performance and quality output waveforms can be improved based on the selection criteria imposed on the scheme. Mechanical vibration and acoustic noise are resulted by the conventional, deterministic PWM methods like Sinusoidal PWM (SPWM) when it is used in drives. An important advantage of random or nondeterministic modulation techniques is non-repetitive spectral characteristics of the output waveforms without energy concentration at distinct harmonics [4]-[7]. Also this period was outstanding due to the revolution of technological possibilities in the field of digital electronic control by micro controller, Digital Signal Processor (DSP), Complex Programmable Logic Devices (CPLD), Field Programmable Gate Array (FPGA) and Application Specific Integrated Circuit (ASIC) technologies. Among all these possibilities, FPGA is a good candidate having the advantage of the flexibility of a programming solution and the efficiency of a specific architecture with a high integration density, and high speed. The Field Programmable Gate Array (FPGA) technology provides Programmable System-On-Chip (PSoC) environments for designing modern digital ASIC controllers for specific applications.

In industrial drives the transferring of harmonic power from the detached spectrum of the output voltage to the unremitting spectrum is achieved by Random Pulse Width Modulation (RPWM) and offers some advantages that are the operation free from an unpleasant acoustic noise and a mechanical vibration [8]-[9]. The existing Random Carrier PWM (RCPWM) schemes result in poor non-deterministic characteristics. They basically use a single-frequency triangular carrier and its inverted version to synthesize the random carrier by a Pseudo-Random Binary Sequence (PRBS) bit selector. In MCBRCPWM scheme utilizes the Non-deterministic characteristics [10]. The switching in random way is centered on a uniform probability density function. The randomly modulated carrier is compared with reference waveform to produce the RPWM pulses. The Space Vector Modulation algorithm for a three-level inverter is used for determining the space vector location and the principle for selecting switching sequences to generate symmetrical PWM output waves. The standard design flow of FPGA implementation and the functional block diagram of FPGA realization are given. The Five-phase sinusoidal PWM signal generator at high-speed sampling frequency using one-chip programmable gate array (FPGA) is made known that the generation of sinusoidal PWM using FPGA can perform the switching frequency of the inverter at 40 kHz switching frequency that may raise potential for excellent drive performances [11]-[12]. The sinusoidal PWM is realized on a single FPGA chip from Xilinx Inc. to provide controlling switching pulses for inverter block. Even though the industrial society has understood the PWM persuaded torque ripples and acoustic noises, the lack of methodical evaluation of existing PWM techniques sojourn the further verdicts. Secondly, the analog platform is inappropriate to non-deterministic PWM methods because of their nature. A flexible, reprogrammable digital platform could solve this issue. A methodical study on performance characteristics such as harmonic spectrum, Total Harmonic Distortion (THD), Harmonic Spread Factor (HSF) and power density spectrum, are presented for both conventional sinusoidal PWM (SPWM) and RPWM. A FPGA based implementation and corroboration of Pseudo Random Binary Sequence (PRBS) bit based Random Carrier PWM (RPWM) for the three-phase voltage Source Inverter (VSI) fed induction motor drive, are presented.

<sup>&</sup>lt;sup>2</sup>Machine Vision and Pattern Recognition Laboratory, Lappeenranta University of Technology, Finland.

## 2. RANDOM CARRIER RPWM

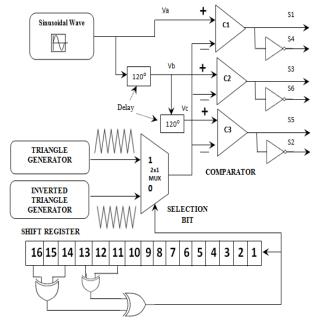

Fig.1. Random Carrier PWM

Fig. 1 shows the randomized triangular carrier generation. As shown in Fig.1, the triangular carrier with fixed frequency 'fc+' and the triangular carriers with fixed frequency but opposite phase 'fc-' are given as input to the  $2\times1$  multiplexer. Both the frequencies (fc+ and fc-) are same. The randomized triangular carrier 'R' can be obtained randomly selecting the fc + and fc- by the PRBS output bits 0 or 1 of the random bit generator. In order to obtain the random bit number for selecting the winning triangle, a triumph sequential digital circuit with large number of distinct states (bigger repetition cycle) is required. This is because the randomness does not rely only on two distinct carriers but also on the sequential pattern used for selection. LFSR is the best solution to offer the above requirement (good randomness). The principle of LFSR is based on the logical operation of several bits of a digital number and is commonly known as pseudo PWM code generator in communication systems [14]. In this paper, 16 bits LFSR with a feedback of four tapings is used and the feedback causes the register to loop through repetitive sequences of pseudo-random value. The choice of taps determines how many values there are in a given sequence before the sequence repeats. The optimum tapping bit numbers are used for logical XOR operation (Bits 4, 5 and 6, 8). Repetition is depends upon the length of LFSR and the clock frequency used. The winning triangle carrier cycle is compared with sinusoidal reference to get the gating pulses.

## 3. SIMULATION

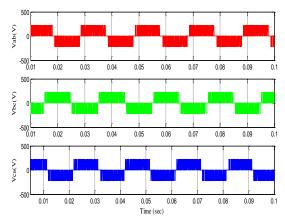

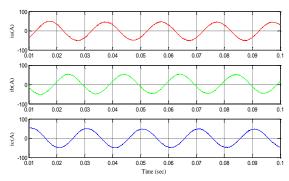

The simulation study is performed in MATLAB/Simulink software. A three-phase VSI inverter with three-phase Squirrel Cage Induction Motor (0.75 kW and 2.5 A load) is considered. The input dc voltage (Vdc) is 415V and the output frequency is taken as 50 Hz. The switching frequency of SPWM is 3kHz while the RPWM employs  $\pm 3$ kHz. The line voltage and current waveforms resulted from SPWM are illustrated in Fig.2 and Fig.3 respectively for modulation index, Ma=0.8.

Fig. 2. Simulated line-line voltage waveform for Ma=0.8

Table 1. Performance of SPWM

| Simulation Results       |                        |         |        |  |  |  |

|--------------------------|------------------------|---------|--------|--|--|--|

| Modulation<br>Index (Ma) | Output Voltage $(V_0)$ | THD (%) | HSF    |  |  |  |

| 0.2                      | 75.26                  | 240.66  | 4.8808 |  |  |  |

| 0.4                      | 136.75                 | 168.02  | 4.6210 |  |  |  |

| 0.6                      | 211.05                 | 122.01  | 4.5554 |  |  |  |

| 0.8                      | 293.75                 | 89.10   | 4.0572 |  |  |  |

| 1.0                      | 367.25                 | 66.07   | 3.6786 |  |  |  |

| 1.2                      | 395.15                 | 58.16   | 3.4591 |  |  |  |

Table 2. Performance of RCPWM

| Simulation Results           |                                     |         |       |  |  |  |

|------------------------------|-------------------------------------|---------|-------|--|--|--|

| Modulati<br>on Index<br>(Ma) | Output<br>Voltage (V <sub>0</sub> ) | THD (%) | HSF   |  |  |  |

| 0.2                          | 49.00                               | 257.92  | 8.262 |  |  |  |

| 0.4                          | 75.81                               | 164.26  | 6.092 |  |  |  |

| 0.6                          | 113.95                              | 121.05  | 5.83  |  |  |  |

| 0.8                          | 153.25                              | 90.55   | 5.516 |  |  |  |

| 0.9                          | 170.25                              | 80.67   | 5.112 |  |  |  |

| 1.0                          | 190.85                              | 68.37   | 4.902 |  |  |  |

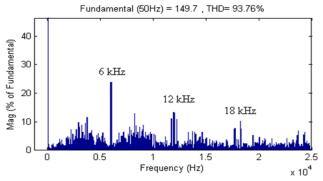

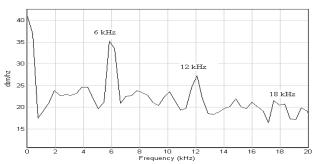

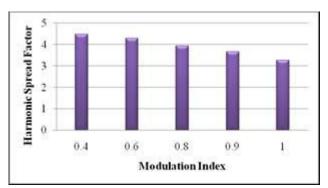

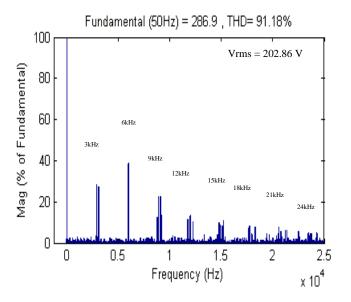

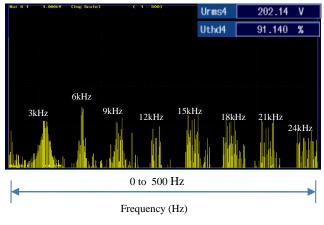

Table 1 describes various performance indices of SPWM. Table 2 presents the results of RCPWM. Fig.4 illustrates the output spectrum output voltage for the RCPWM and the power density spectrum is depicted in Fig.5. The bar chart drawn in Fig.6 exhibits the modulation depth dependency of HSF.

Fig. 3. Simulated line current waveform for Ma=0.8

Fig. 4. Spectrum of output voltage

Fig. 5. Power spectral density for Ma= 0.8

Fig. 6. RPWM Harmonic Spread Factor and Modulation Index

Fig. 7. Hardware implementation

## 4. HARDWARE IMPLEMENTATION

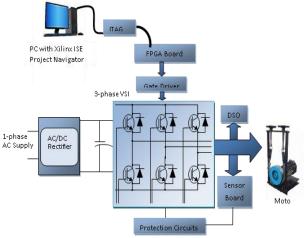

The proposed Random Carrier PWM architecture has been designed using the VHDL language. The functional

simulation of the architecture has been carried out using the tool Modelsim 6.3. The Register Transfer Level (RTL) level verification and implementation are done using the synthesize tool Xilinx ISE 13.2. Then the designed architecture has been configured to the SPARTAN-6 FPGA (XC6SLX45) device. Hardware implementation is shown below

#### **Device Utilization Summary (estimated values) Logic Utilization Available** Utilization Used Number of Slice Registers 325 30064 1% Number of Slice LUTs 793 15032 5% Number of fully used 228 890 25% LUT-FF pairs Number of bonded IOBs 10 186 5% Number of BUFG / BUFG 5 16 31% **CTRLs** Number of DSP48A1s 3 38 7%

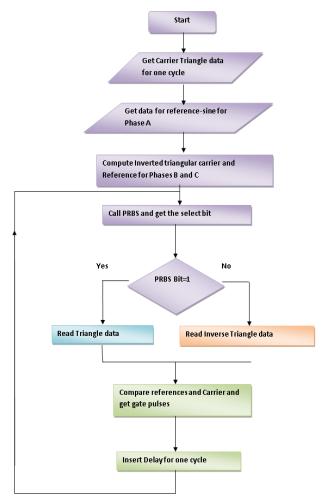

The algorithm involved in the RCPWM implementation is diagrammed in Fig.7. The triangular data is initialized first

and inverse triangular data is derived from it. From the fed sine reference data of 'A' phase, data from 'B' and 'C' phases are derived. Now the called LSFR sequence select between the carriers and its comparison with the reference results in required pulses for the VSI. The simulated VHDL Design of the RCPWM architecture is synthesized using Xilinx ISE software. The RTL verification and logic implementation of the design are carried out here. The corresponding synthesis results are shown in Fig10. The power estimation for the designed architecture has been done using the Xilinx power estimator tool (Xpower Estimator (XPE)-14.1).

Fig. 8. MATLAB Simulation Results

The synthesized design of RCPWM architecture is downloaded to the FPGA Spartan 6 device (XC6SLX45) with the help of device programming software "DIGILENT ADEPT". The configured FPGA device with proposed architecture has been tested with a prototype of three phase VSI with an input dc voltage (Vdc) of 400V and a load of 0.75 kW three-phase Squirrel Cage Induction Motor. The triumph of the devolved code is proved by the results presented in Fig.8 and Fig.9, which are simulation and hardware harmonic spectra. The hardware setup is shown in Fig.10.

Fig. 9. Hardware Results

Fig. 10. Experimental setup

Table 3. Comparison of Simulation and Hardware Results-RCPWM

|                                           | Simulation<br>Results |         | Hardware<br>Results   |            |

|-------------------------------------------|-----------------------|---------|-----------------------|------------|

| Modulatio<br>n Index<br>(M <sub>a</sub> ) | o/p<br>Voltage<br>(V) | THD (%) | o/p<br>Voltage<br>(V) | THD<br>(%) |

| 0.2                                       | 49.13                 | 255.68  | 47.51                 | 246.89     |

| 0.4                                       | 103.47                | 161.54  | 103.89                | 101.88     |

| 0.6                                       | 151.34                | 122.19  | 151.63                | 120.88     |

| 0.8                                       | 203.92                | 91.27   | 202.63                | 91.47      |

| 0.9                                       | 227.21                | 80.56   | 228.08                | 79.339     |

| 1.0                                       | 253.58                | 69.08   | 255.17                | 67.02      |

## 5. CONCLUSION

Induction motors are mainly employed in industrial processes and become dominant Adjustable Speed Drive (ASD). The performance of the induction drive depends largely on PWM techniques employed. Random PWM is widely used to spread the harmonic power, and hence reduce the torque ripples and acoustic noises of the ASDs. The proposed architecture of RCPWM is the effective solution for the acoustic noise in the Adjustable Speed Drives. The results such as device utilization summary, power estimation and temperature dependency are very useful for the handling of digital device used for the control purpose. The ability of the RPWM for harmonic power spreading is validated by the simulation study while the accurate imitation of the RPWM in FPGA platform is confirmed by the hardware results. The RCPWM offers higher output voltage, lesser THD and minimal HSF than the SPWM for the entire working range.

## APPENDIX

| Power (P)               | 0.75kW     |

|-------------------------|------------|

| Line- Line Voltage (VL) | 415 V      |

| Frequency (f)           | 50 Hz      |

| Stator Resistance (Rs)  | 4350       |

| Stator Inductance (Ls)  | 5839Н      |

| Rotor Resistance (Rr)   | 1.395O     |

| Rotor Inductance (Lr)   | 0.005839Н  |

| Inertia (J)             | 0.0131Kgm2 |

| Friction factor         | 0.0029Nms  |

| Pole Pairs              | 2          |

## REFERENCES

- [1] VikramKaura and Vladimir Blasko, "A new method to extend linearity of a sinusoidal PWM in the over modulation region," *IEEE Transaction on Industry Applications*, vol.32, no.5, pp.1115-1121, Sep./Oct., 1996.

- [2] Ahmet M. Hava, Russel J. Kerkman, and Thomas A. Lipo, "Carrier-Based PWM-VSI Over modulation Strategies: Analysis, Comparison, and Design," *IEEE Transactions on Power Electronics*, vol. 13, no. 4, pp.674-689, July 1998.

- [3] Michael A. Boost, and Phoivos D. Ziogas, "State -of -Art- Carrier PWM Techniques: A Critical Evaluation," *IEEE Transactions Industry Applications*, Vol.24, No.2, pp.271-280 March/April 1998.

- [4] Jarin T, Subburaj P "Behaviour of Non- deterministic PWM Methods and Influence of DC Link Fluctuation in Harmonic Spreading Effect of VSI Output Voltage Spectrum" *International Journal of Applied Engineering Research*, Vol. 10 No.20., pp. 2110-2115, (2015).

- [5] V.G. Agelidis, and D. Vincenti, "Optimum Non-Deterministic Pulse Width Modulation for Three-phase Inverters," *in Conf. Rec. IEEE IECON* 1993.

- [6] Jarin T, Subburaj P "Comprehensive Investigation on Harmonic Spreading Effects of SPWM and RPWM Methods" *European Journal of Scientific Research*. Vol. 103 No 2 June, 2013, pp.296 303.

- [7] A. M. Trzynadlowski, S. Legowski, and R. L. Kirlin, "Random pulse width modulation technique for voltage controlled power inverters," in *Conf. Rec. IEEE—IAS Annu. Meeting*, 1987, pp. 863–868.

- [8] T. Jarin, P. Subburaj and Shibu J V Bright "A Ripple Rejection Inherited RPWM for VSI Working with Fluctuating DC Link Voltage" *Journal of Electrical Engineering & Technology.2015; 10(5): 709-718.*

- [9] T. Jarin, P. Subburaj and Shibu J V "Performance Evaluation and Experimental Validation of Random Pulse Position Pwm for Industrial Drives" *African Journal of Basic & Applied Sciences vol.7, no.3, pp.137-146, 2015.*

- [10] Sivarani T.S., Joseph Jawhar S., Agees Kumar C. "Intensive random carrier pulse width modulation for induction motor drives based on hopping between discrete carrier frequencies", *IET Power Electronics*.

- [11] Yun Wan and Jianguo Jiang, "The study of FPGA-based three-level SVM NPC inverter", *Proceedings of IEEE 6th International Power Electronics and Motion Control Conference (IPEMC '09)*, pp.- 1470 1474, 2009. Wuhan.

- [12] Sutikno, T.et. al., "FPGA based five-phase sinusoidal PWM generator", *Proceedings of IEEE International Conference on Power and Energy (PECon-2012)*, pp.314 318, 2012, Kota Kinabalu.

- [13] Alfonso Carlosena, Wing-Yee Chu, Bertan Bakkaloglu, and SayfeKiaei," Randomized Carrier PWM With Exponential Frequency Mapping", *IEEE Transactions on Power Electronics*, Vol.22, no.3, pp-960-966May 2007.

- [14] S.Y.R. Hui, I.Oppermann, F. Pasalic and Sathiakumar, "Microprocessor-based Random PWM Schemes for DC-AC Power Conversion", 0-7803-2730-6/95©1995 IEEE.

**60** | P a g e Online ISSN: 2456-883X Publication Impact Factor: 0.825 Website: www.ajast.net